# MSP430F15x/16x/161x Device Errata Sheet Current Version

Note: See Appendix for prior revisions

## Package Markings

#### PM64: LQFP(PM) 64-pin

| <b>W</b> YMLLLLS | YM<br>LLL | = Year and Month Date Code<br>L = LOT Trace Code |

|------------------|-----------|--------------------------------------------------|

| M430Fxxx         | S         | = Assembly Site Code                             |

| REV #            | #         | = DIE Revision                                   |

| 0                | 0         | = PIN 1                                          |

### RTD64: QFN(RTD) 64-pin

| O <sub>M430Fxxx</sub> |             | = TI<br>= Year and Month Date Code<br>_ = LOT Trace Code |

|-----------------------|-------------|----------------------------------------------------------|

| TI YMS<br>LLLL #      | S<br>#<br>0 | = Assembly Site Code<br>= DIE Revision<br>= PIN 1        |

### **Detailed Bug Description**

CPU4 - Bug description:

Module: CPU, Function PUSH #4, PUSH #8

The single operand instruction PUSH cannot use the internal constants (CG) 4 and 8. The other internal constants (0, 1, 2, -1) can be used. The Assembler version 1.08 and higher produces correct code. The number of clock cycles is different: PUSH #CG uses address mode 00, requiring 3 cycles, 1 word instruction PUSH #4/#8 uses address mode 11, requiring 5 cycles, 2 word instruction

Workaround implemented in assembler. No fix planned.

I2C7 - Bug description:

Module: USART (I2C Mode): ARDYIFG Interrupt flag is not generated.

When the USART is configured for I2C communication (U0CTL[5]=1, U0CTL[2]=1, U0CTL[0]=1) and the I2C is configured as a system slave (U0CTL[1]=0), the ARDYIFG interrupt flag generation can fail to generate, even when both the Stop condition is received and the receive buffer is empty. This condition occurs when the I2C clock source, selected by I2CTCTL[5-4], is disabled by the Status Register (SR) control signals OSCOFF or SCG1.

In this configuration, the hardware clock activation is enabled by the I2C module. However, if RXRDYIFG is polled for data buffer reception, the I2C hardware clock activation may be disabled before the ARDYIFG is generated.

Workaround:

Solution #1: Use interrupt service routines via the I2C\_IV to handle all I2C interrupts. Solution #2: After detection of I2C Own Address (OAIFG), the selected I2C clock source is enabled by clearing the OSCOFF or SCG1 Status Register (SR) bits. When the ARDYIFG is detected, the OSCOFF or SCG1 in the Status Register (SR) can be set to disable the clock source and return to the desired low power mode operation. Solution #3: For slave only devices, it is normally not necessary to use ARDYIFG.

TA12 TA12 - Bug description (same as TB2):

Module: TimerA, Interrupt is lost (slow ACLK)

TimerA counter is running with slow clock (external TACLK or ACLK) compared to MCLK. The compare mode is selected for the capture/compare channel and the CCRx register is incremented by 1 with the occurring compare interrupt (if TAR = CCRx). Due to the fast MCLK the CCRx register increment (CCRx = CCRx+1) happens before the TimerA counter has incremented again. Therefore the next compare interrupt should happen at once with the next TimerA counter increment (if TAR = CCRx + 1). This interrupt gets lost.

Workaround:

Switch capture/compare mode to capture mode before the CCRx register increment. Switch back to compare mode afterwards.

### Detailed Bug Description (continued)

TB2 TB2 - Bug description (same as TA12):

Module: TimerB, Interrupt is lost (slow ACLK)

TimerB counter is running with slow clock (external TBCLK or ACLK) compared to MCLK. The compare mode is selected for the capture/compare channel and the CCRx register is incremented by 1 with the occurring compare interrupt (if TBR = CCRx). Due to the fast MCLK the CCRx register increment (CCRx = CCRx+1) happens before the TimerB counter has incremented again. Therefore the next compare interrupt should happen at once with the next

TimerB counter increment (if TBR = CCRx + 1). This interrupt gets lost.

Workaround: Switch capture/compare mode to capture mode before the CCRx register increment. Switch back to compare mode afterwards.

US15 - Bug description:

Module: USART0, USART1, Function: UART receive with two stop bits

USART hardware does not detect a missing second stop bit when SPB = 1. The Framing Error Flag (FE) will not be set under this condition and erroneous data **reception may occur**.

Workaround: None (Configure USART for a single stop bit, SPB = 0)

#### WDG2 - Bug description:

If a key violation is caused by erroneously accessing a flash control register, the watchdog interrupt flag is set in addition to a correctly generated PUC.

Workaround: None

SLAZ018A - MAY 2005

# Appendix: Prior Versions

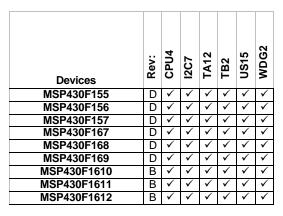

|             |        | 14           | 7            | 32       | 12           | Q            | 14          | 15           | WDG2         | XOSC4        |

|-------------|--------|--------------|--------------|----------|--------------|--------------|-------------|--------------|--------------|--------------|

| Devices     | Rev:   | CPU4         | 12C7         | SVS2     | TA12         | TB2          | <b>US14</b> | US15         | Š            | ×            |

|             | D      | ✓            | $\checkmark$ |          | $\checkmark$ | $\checkmark$ |             | $\checkmark$ | $\checkmark$ |              |

| MSP430F155  | С      | ✓            | ✓            | ✓        | $\checkmark$ | $\checkmark$ | ✓           | $\checkmark$ | ✓            |              |

|             | В      | ✓            | ✓            | ✓        | ✓            | ✓            | ✓           | ✓            | ✓            | $\checkmark$ |

|             | D      | ~            | ✓            |          | $\checkmark$ | $\checkmark$ |             | $\checkmark$ | ✓            |              |

| MSP430F156  | С      | ~            | $\checkmark$ | ✓        | ✓            | ✓            | ✓           | ✓            | $\checkmark$ |              |

|             | В      | ✓            | ✓            | ✓        | $\checkmark$ | $\checkmark$ | ✓           | $\checkmark$ | ✓            | ✓            |

|             | D      | ✓            | ✓            |          | ✓            | ✓            |             | ✓            | ✓            |              |

| MSP430F157  | С      | ✓            | ✓            | ✓        | ✓            | ✓            | ✓           | ✓            | ✓            |              |

|             | В      | ✓            | ✓            | ✓        | ✓            | ✓            | ✓           | ✓            | ✓            | ✓            |

|             | D      | ✓            | ✓            |          | ✓            | ✓            |             | ✓            | ✓            |              |

| MSP430F167  | С      | ✓            | ✓            | ✓        | ✓            | ✓            | ✓           | ✓            | ✓            |              |

|             | В      | ✓<br>✓       | ✓<br>✓       | ✓        | ✓<br>✓       | ✓<br>✓       | ✓           | ✓<br>✓       | ✓<br>✓       | ✓            |

| MSP430F168  | D<br>C | ✓<br>✓       | ✓<br>✓       | <b>√</b> | ✓<br>✓       | ✓<br>✓       | <b>√</b>    | ✓<br>✓       | ✓<br>✓       |              |

| WI3F430F100 | B      | ▼<br>√       | ✓<br>✓       | v<br>√   | ▼<br>✓       | ✓<br>✓       | v<br>√      | ✓<br>✓       | v<br>√       | ~            |

|             | D      | ·<br>~       | ·<br>~       | Ľ.       | •<br>•       | •<br>•       | Ľ.          | •<br>•       | ·<br>~       |              |

| MSP430F169  | C      | ·<br>√       | ·<br>•       | ✓        | ·<br>✓       | ✓            | ✓           | ·<br>✓       | ·<br>•       |              |

|             | B      | ~            | ~            | ✓        | $\checkmark$ | $\checkmark$ | ✓           | $\checkmark$ | ~            | ~            |

|             | В      | ✓            | ✓            | -        | ✓            | ✓            | -           | ✓            | ✓            | <u> </u>     |

| MSP430F1610 | A      | ✓            | ✓            | ✓        | ✓            | ✓            | ✓           | ✓            | ✓            |              |

| MCD420F4C44 | В      | ✓            | ✓            |          | ✓            | ✓            |             | ✓            | ✓            |              |

| MSP430F1611 | Α      | ✓            | ✓            | ✓        | ✓            | ✓            | ✓           | ✓            | ✓            |              |

| MSP430F1612 | В      | ✓            | ✓            | l        | ✓            | ✓            | l           | ✓            | ✓            | 1            |

| 1012        | Α      | $\checkmark$ | $\checkmark$ | ✓        | $\checkmark$ | $\checkmark$ | ✓           | $\checkmark$ | $\checkmark$ |              |

### **Detailed Bug Description**

**SVS2** SVS2 - Bug description:

Module: SVS, DAC1: DAC1 overrides the input of the SVS comparator

DAC1 overrides the input of the SVS comparator. This is caused by a conflict between SVS and DAC1 at Port 6.7. DAC1 is enabled when DAC12AMPx is > 0.

Workaround: Do not enable DAC1 when the SVS is used.

US14 - Bug description:

Module: USART0, USART1, UART Mode: Lost character start edge

When using the USART in UART mode with UxBR0 = 0x03 & UxBR1 = 0x00, the start edge of received characters may be ignored due to internal timing conflicts within the UART state machine. This condition does not apply when UxBR0 is > 0x03.

Workaround: None

**XOSC4** XOSC4 - Bug description:

Module: XT1: XT1 high frequency oscillator low power wake-up error

The XT1 high frequency oscillator wake-up from low power mode operation is not functional.

Workaround: If using the XT1 high frequency oscillator circuitry (XTS, BCSCTL1[6] = 1), the OSCOFF bit in the Status Register (SR) must always = 0.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address:

Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2005, Texas Instruments Incorporated